트랜지스터와 연산 증폭기 등의 전기소자들을 이해하고, 전기회로 실습을 통해 소자 및 실험에 관련된 장비의 사용법을 습득한다.

연산증폭기(Operational Amplifier)

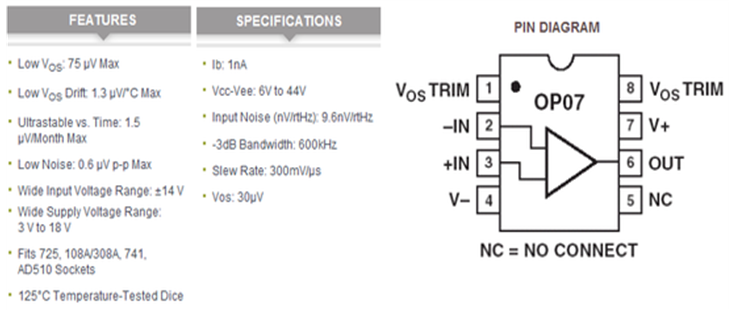

아날로그 계산기에서 수학적 ‘연산(operation)’을 수행하는데 쓰였기 때문에 붙여진 이름으로, 근래에 들어 그 용도가 넓어지고 모노리식 제조길수에 의해 값이 싸짐에 따라 실질적으로 전자공학의 모든영역에 확산되어 이용되고 있다. 연산 증폭기란 매우 높은 이득을 가진 하나의 직결 증폭기이며, 외부적 귀환을 이용하여 그 이득과 임피던스 특성을 제어하도록 한 것이다.

연산 증폭기를 구성하고 있는 내부의 트랜지스터의 경우 각각의 제조공정에 발생하는 오차를 가지고 있으며, 1번 핀과 8번 핀에 연결된 저항 R_offset의 기능은 이러한 오차를 조절하여 정밀한 입출력을 가진 연산증폭기 회로를 구성할 수 있도록 해준다. 일반적으로 두 개의 입력이 같은 상태에서 출력 값이 ‘0’으로 떨어지는 순간까지 R_offset을 조정하여 사용한다. 현재 생산되는 연산증폭기의 대부분은 offset기능을 제공하고 있으며, 출고 전이미 offset에 대한 조절이 완료된 상태로 판매되고 있는 연산 증폭기도 있다.

실험 방법

1. 실험 과정

1) Logic Lab unit에 장착된 브레드 보드를 이용하여 회로를 구성한다

2) 연산전원 공급은 ±12V를 사용하도록 하며, 함수 발생기를 사용하여 ±1V의 구형파 입력신호를 생성한다.

3) 증폭도 조절을 위하여 저항 Ri 는 1kΩ으로 고정하고 Rf의 값을1kΩ으로 한다.

4) 함수 발생기의 출력을 입력하였을 경우의 출력 전압을 측정한다.

5) Rf의 크기를 적절하게 변화시켜가며 Rf의 변화에 따른 출력 전압을 측정

[회로기초실험]연산 증폭기 레포트

1.1. 연산증폭기(Operational Amplifier) 아날로그 계산기에서 수학적 ‘연산(operation)’을 수행하는데 쓰였기 때문에 붙여진 이름으로, 근래에 들어 그 용도가 넓어지고 모노리식 제조길수에 의해 값이

www.happycampus.com

댓글